与预充电不同的时,刷新操作是一个定时的操作,间隔一段时间后,必须执行一次。目前SDRAM的存储电容的刷新周期最大为64ms,由于自刷新指令一次只能刷新一行,因此我们要在64ms内刷新完所有行。如果SDRAM的行数为4096...

”fpga sdram“ 的搜索结果

用Verilog语言实现SDRAM的初始化配置和读、写、刷新的操作,带Modelsim仿真模块

FPGA——初识SDRAM

标签: fpga开发

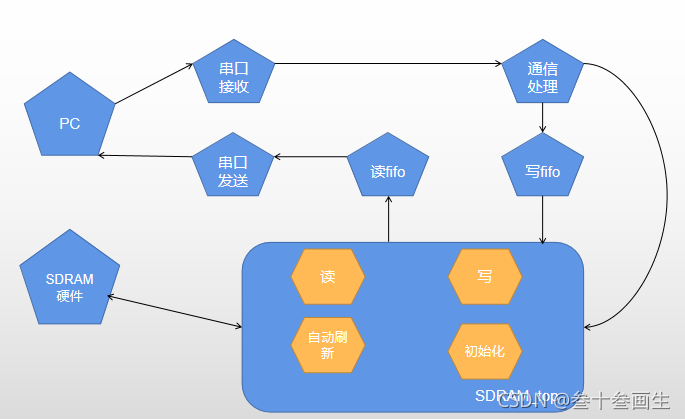

FPGA SDRAM控制程序可直接使用,用两个fifo封装

sdram_howeveryt5_sdram_SDRAM封装成fifo_FPGASDRAM.zip

0_19_Sdram_Control_VERILOGSDRAM_theels1_FPGAverilog_FPGASDRAM.zi

sdram_howeveryt5_sdram_SDRAM封装成fifo_FPGASDRAM_源码.rar.rar

FPGASDRAM是指在FPGA(Field-Programmable Gate Array)中使用SDRAM(Synchronous Dynamic Random-Access Memory)的技术。FPGA是一种可编程逻辑器件,而SDRAM是一种常见的存储器类型,用于存储数据。 在FPGA中使用...

FPGA驱动SDRAM

标签: fpga开发

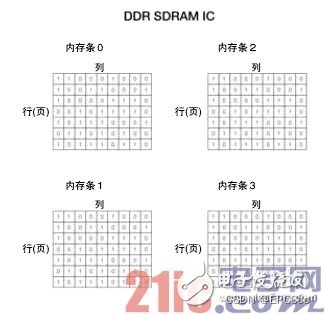

SDRAM(同步动态随机存取存储器)。

FPGA对SDRAM的控制实现

标签: fpga

如果对SDRAM原理以及时序不是很了解的朋友,推荐看一下如下这篇文章: SDRAM-高手进阶,终极内存技术指南——完整进阶版 *****************************************GO*********************************** ...

VPM642采用TL16C752B通用异步收发器UART,其上包含两路相互独立的异步收发器,接受和发送各带64字节FIFO,并且各自带有Modem接口信号,最高传输速率为1.5Mbps 在VPM642中,TL16C752B(以下简称752B)与EMIFA之CE1...

在FPGA开发中,使用DDR SDRAM IP核可以方便地集成DDR SDRAM控制器到设计中。在"Diagram"视图中,右键单击DDR SDRAM IP核并选择"Make External",以将其暴露为顶层端口。在左侧的"IP Integrator"视图中,右键单击...

推荐文章

- linux md5 加密字符串和文件方法_aes-128-cbc md5-程序员宅基地

- [论文笔记]彻底讲透U-net医学影像分割-小样本_医学小样本-程序员宅基地

- [软件安装] Halcon联合VC配置及例程_c++ halcon 附加到进程-程序员宅基地

- 推荐很不错的typecho资源下载类主题_typecho资讯主题-程序员宅基地

- PID循迹控制算法_循迹算法-程序员宅基地

- Python 进程+协程并发小练习 假设10w个url地址每个请求1秒尝试用4个进程每个进程开启1000个协程去请求统计运行时间_python每秒并发1000个请求-程序员宅基地

- 微信小程序在线考试系统 毕业设计(1)首页_考试小程序首页代码-程序员宅基地

- Java实现“扑克牌游戏”底层逻辑_利用数组随机生成扑克牌-程序员宅基地

- JavaScript循环_js用户登录验证限制次数while循环做法-程序员宅基地

- 图像分割FCN全卷积神经网络_cloudfcn-程序员宅基地